激发创“芯”潜力,EDA精英挑战赛概伦电子赛题发布

2024-08-05

近日,2024中国研究生创“芯”大赛·EDA精英挑战赛正式拉开帷幕。作为国内首家EDA上市公司,关键核心技术具备国际市场竞争力的EDA领军企业,同时也是集成电路设计自动化(EDA)产教融合联盟常务理事单位,概伦电子一直秉持与中国集成电路产业共同成长的理念,长期致力于为中国集成电路产业打造多层次的专业人才培养机制,已连续六年支持和参与该项赛事。本次概伦电子全新发布“数字电路仿真中组合逻辑环路分析”企业赛题,欢迎广大同学们踊跃报名!

赛题名称

数字电路仿真中组合逻辑环路分析

赛题背景

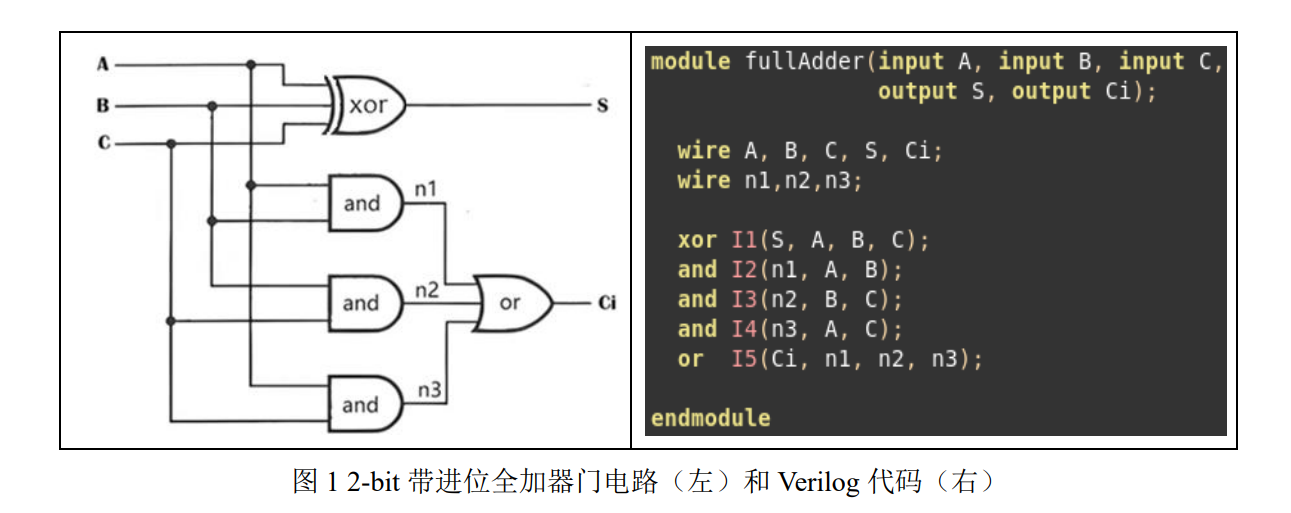

用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。常用的门电路在逻辑功能上有与门、或门、非门、与非门、或非门、异或门、异或非门等几种。通常门电路为多输入、单输出结构,多个门电路按照一定规则组合在一起可实现具有特定功能的组合逻辑电路,例如下图为 2-bit 带进位全加器的门级电路图和 Verilog 代码。

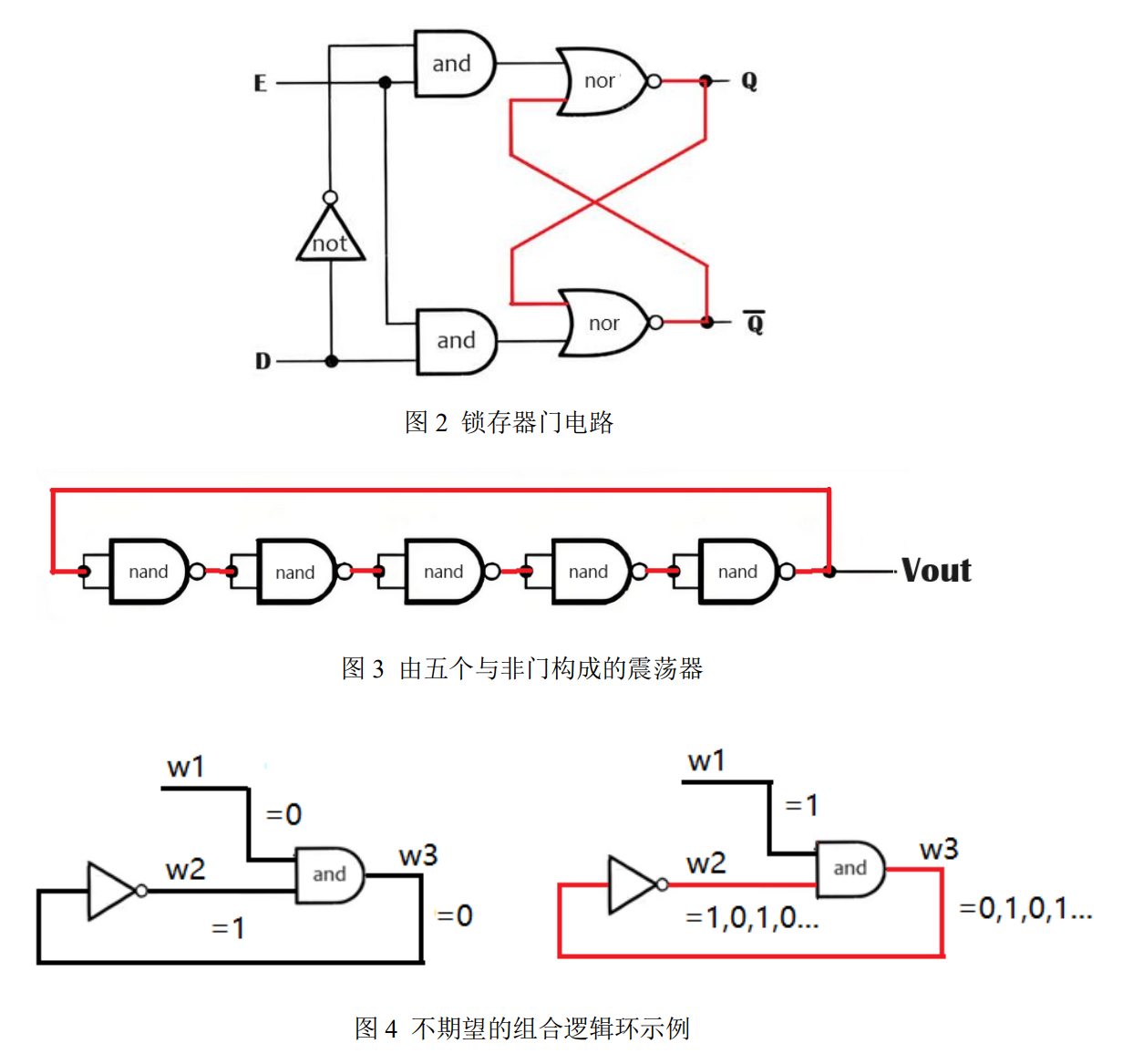

在组合逻辑电路中,起始于某个组合逻辑单元经过一串组合逻辑又回到起始组合逻辑单元的逻辑环路称为组合逻辑环路。组合逻辑环路分为正向反馈和负向反馈两种类型。正向反馈环路是指能够维持当前组合逻辑输出信号状态不变的反馈,常见于锁存器、寄存器和 SRAM 存储器单元等电路中。负向反馈环路是指将当前组合逻辑输出信号翻转的反馈,负向反馈环路会导致输出信号值不停翻转,常见于振荡器、伪随机数生成器等电路中。图 2 和图 3 为锁存器和振荡器门电路,其中红色信号线为锁存器和振荡器门电路中的组合逻辑环路部分。图 4 为不期望的组合逻辑环的示例图,当 w1 为 0 时,w2 为 0,w3 为 1;当 w1 为 1 时,w2 和 w3 将产生震荡。

组合逻辑环路常见于基本的门电路模块中,但在大部分数字电路设计应用场景中都不需要使用组合逻辑环路。不符合预期的组合逻辑环路可能导致多重驱动或信号震荡,导致电路功耗增加和功能错误。组合逻辑环难以被静态时序分析工具分析和计算,可能导致仿真器进入死循环。自动检测数字门电路中的不符合预期的组合逻辑环,分析触发条件和提供断开环路最小路径,帮助设计人员发现设计问题,是 EDA 工具需要解决的问题。

检测数字门电路中的组合逻辑环路需要获取门电路的拓扑结构和逻辑门信息,可通过 Verilog 仿真器的 VPI 接口实现。Verilog 语言标准支持使用 VPI(Verilog Procedural Interface)编程语言接口与 C 语言程序交互,VPI 接口提供了一套 C 语言函数,通过这些 C 语言函数可以获取 Verilog 网表的器件连接关系和行为逻辑,并且可访问和修改仿真阶段的信号值。所有 Verilog 仿真器都支持 VPI 接口,在仿真器仿真阶段,通过 VPI 接口可获取网表中逻辑门及其信号连接信息,通过这些信息可构建完整逻辑门电路信息。

赛题Chair介绍

祁仲东

西安电子科技大学

西安电子科技大学准聘副教授。2009年和2015年在清华大学计算机科学与技术系获得学士学位和博士学位,并在加州大学河滨分校做博士后,获得2014年ICCD会议最佳论文提名,指导学生获2020年集成电路EDA精英挑战赛最高奖麒麟杯,ICCAD 2020竞赛(问题B)第三名,ISPD 2021竞赛Honorable Mention。

赛题描述

请查看完整版赛题描述:

![]() 2024中国研究生创芯-EDA精英挑战赛赛题指南_概伦电子.pdf

2024中国研究生创芯-EDA精英挑战赛赛题指南_概伦电子.pdf

大赛概况

2024中国研究生创“芯”大赛·EDA精英挑战赛赛程时间安排如下:

奖项设置

*具体详见大赛官方通知